Layout of cascade current mirrors

Netlist;

* SPICE3 file created from hwk5.ext -

technology: scmos

.MODEL nfet NMOS LEVEL=3 PHI=0.600000

TOX=2.1200E-08

+ XJ=0.200000U TPG=1 VTO=0.7860

DELTA=6.9670E-01

+ LD=1.6470E-07 KP=9.6379E-05 UO=591.7

THETA=8.1220E-02

+ RSH=8.5450E+01 GAMMA=0.5863

NSUB=1.6160E+16

+ NFS=5.0000E+12 VMAX=2.0820E+05

ETA=7.0660E-02

+ KAPPA=1.3960E-01 CGDO=4.0241E-10

CGSO=4.0241E-10

+ CGBO=3.6144E-10 CJ=3.8541E-04 MJ=1.1854

+ CJSW=1.3940E-10 MJSW=0.125195

PB=0.800000

M1000 m0 m0 A Gnd nfet w=4 l=3

+ ad=29 pd=22 as=58 ps=44

M0001 Vx m0 B Gnd nfet w=20 l=3

+ ad=140 pd=54 as=280 ps=108

M1002 B A Gnd Gnd nfet w=20 l=3

+ ad=0 pd=0 as=169 ps=76

M1003 Gnd A A Gnd nfet w=4 l=3

+ ad=0 pd=0 as=0 ps=0

C0 Gnd 0 8.7fF

C1 m0 0 16.8fF

Iref Vdd m0 100µA

V1 Vdd 0 5V

Vx Vx 0 5V

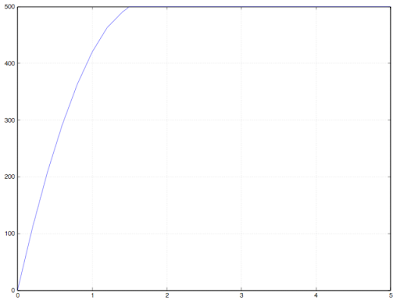

Results;

No comments:

Post a Comment